新的Volta GPU架构的显著特征是它的Tensor Core,新的Tensor Core是专门为深度学习设计的,有助于提高训练神经网络所需的性能。Tesla V100的Tensor Core能够为训练、推理应用提供120Tensor TFLOPS.相比于在P100 FP32上,在Tesla V100上进行深度学习训练有12倍的峰值TFLOPS提升。而在深度学习推理能力上,相比于P100 FP16 运算,有了6倍的提升。

在许多深度学习框架(包括Tensorflow,PyTorch,MXNet和Caffe2)中Tensor Core已经被支持用于深度学习培训。有关在使用这些框架时启用Tensor Core的更多信息,请参阅Mixed-Precision Training Guide

在深度学习推理方面,最近的TensorRT 3版本也支持Tensor Core.

Tensor Core为卷积和矩阵运算提供了巨大的推动力。 Tensor内核可以使用NVIDIA库进行编程,并直接使用CUDA C ++代码

什么是Tensor Cores?

每个 Tensor Core 包含一个 4x4x4 的矩阵处理阵列来完成 D=A x B + C 的运算,其中 A、B、C、D 是 4×4 的矩阵,如下图所示。矩阵相乘的输入 A 和 B 是 FP16 矩阵,相加矩阵 C 和 D 可能是 FP16 矩阵或 FP32 矩阵。

Tensor Core 的 4x4x4 矩阵乘法与累加

每个 Tensor Core 每个时钟可执行 64 次浮点 FMA 混合精度运算(FP16 乘法与 FP32 累加),一个 SM 单元中的 8 个 Tensor Core 每个时钟可执行共计 1024 次浮点运算。相比于使用标准 FP32 计算的 Pascal GP100 而言,单个 SM 下的每个深度学习应用的吞吐量提升了 8 倍,所以这最终使得 Volta V100 GPU 相比于 Pascal P100 GPU 的吞吐量一共提升了 12 倍。Tensor Core 在与 FP32 累加结合后的 FP16 输入数据之上操作。FP16 的乘法得到了一个全精度结果,该结果在 FP32 和其他给定的 4x4x4 矩阵乘法点积的乘积运算之中进行累加。

Volta GV100 Tensor Core 流程图

在程序执行期间,多个 Tensor Core 通过一组 warp 线程的执行而同时使用。warp 内的线程提供了 Tensor Core 来处理大型 16×16×16 矩阵运算。CUDA 将这些操作作为 Warp-Level 矩阵运算在 CUDA C++ API 中公开。这些 C++接口提供了专门化的矩阵负载,如矩阵乘法和累加,矩阵存储操作可以有效地利用 CUDA C++程序中的 Tensor Core。

Tesla V100:

人工智能计算和 HPC 的助推器

毫无疑问,全新的英伟达 Tesla V100 加速器是世界上性能最高的并行处理器,旨在为计算量最大的 HPC 设备、人工智能和图形工作任务提供支持。

它的核心 GV100 GPU 包含 211 亿个晶体管,而芯片面积为前所未有的 815 平方毫米(Tesla GP100 为 610 平方毫米)。它采用了台积电(TSMC)的 12nm FFN 专属工艺打造。与其前身 GP100 GPU 及其他 Pascal 架构的显卡相比,GV100 提供了更强的计算性能,并增加了许多新功能。它进一步减小了 GPU 编程和应用程序移植难度,也通过制程的升级提高了 GPU 资源利用率。另外,GV 100 也是一款能效极高的处理器,其在单位功耗的性能上表现卓越。下图给出了 ResNet-50 深度神经网络在 Tesla V100 上进行训练的性能表现。

对于 12nm 制程的选择(AMD 准备在 2018 年推出使用 7nm 制程的显卡),英伟达的首席工程师表示他们已在功耗和性能之间做出了最佳选择。

Tesla V100 在 ResNet-50 深度神经网络训练任务中的速度比 Tesla P100 快 2.4 倍。如果每张图像的目标延迟是 7ms,那么 Tesla V100 使用 ResNet-50 深度神经网络进行推理的速度比 P100 快 3.7 倍(参与测试的 V100 为原型卡)。

Tesla V100 的主要计算特征

为深度学习优化过的新型流式多处理器(SM)架构。Volta 对 GPU 核心的 SM 处理器架构进行了重要的重新设计。新的 Volta SM 架构比前代 Pascal 设计能效高 50%,在同样的功率范围下 FP32 和 FP64 性能有重大提升。新的 Tensor Core 是专门为深度学习设计的,为浮点运算速度带来了 12 倍的提升。有了独立的、并行的整型和浮点型数据通路,Volta SM 在负载上也更高效,混合了计算与地址运算。Volta 新的独立线程调度能力使得并行线程之间的细粒度同步协同(finer-grain synchronization and cooperation)成为可能。最终,新型的 L1 Data Cache 与 Shared Memory 子系统的结合也能极大地提升性能,同时还简化了编程。

第二代 NVLink。第二代英伟达 NVLink 高速互连技术能提供更高的带宽、更多连接,同时还改进了多 GPU 和多 GPU/CPU 系统配置的延展性。

HBM2 显存:更快、更高效。Volta 高度调整的 16GB HBM2 显存子系统提供了 900 GB/s 的峰值显存带宽。来自三星的新一代 HBM2 显存和 Volta 中的新一代显存控制器的组合实现的显存带宽是 Pascal GP100 的 1.5 倍,而且在许多负载上的显存带宽效率更高。

Volta 多处理服务。Volta 多服务处理(MPS:Multi-Process Service)是 Volta GV100 的一项新特性,能够为 CUDA MPS 服务器的关键组件提供硬件加速,从而能为共享该 GPU 的多个计算应用提供更高的性能、隔离和更好的服务质量(QoS)。Volta MPS 还将 MPS 客户端的最大数量从 Pascal 的 16 提升到了 Volta 的 48。

增强统一存储和地址转换服务。Volta GV100 中的 GV100 统一存储(GV100 Unified Memory)技术包括新型访问计数器,让访问网页最频繁的处理器能更准确的迁移存储页。

协作组(Cooperative Groups)和新的 Cooperative Launch API。协作组是 CUDA 9 中新的编程模型,用来组织通信线程组。Volta 增加了对新型同步模式的支持。

·

最大性能和最大效率模式。在最大性能模式下,Tesla V100 加速器将不受限制的把 TDP(热设计功耗)水平提高到 300W,从而加速需要最快计算速度和最高数据吞吐的应用。最大效率模式下,数据中心管理员可以调整 Tesla V100 加速器的功率使用,从而用单位功耗下最优的性能进行运算。

为 Volta 优化过的软件。Caffe2、MXNet、CNTK、TensorFlow 等这样的深度学习框架的新版本,能够利用 Volta 的性能来获得更快的训练速度、更高的多节点训练性能。GPU 加速库(比如 cuDNN、cuBLAS 等)的 Volta 优化版本利用 Volta GV100 架构的新特性能为深度学习和高性能计算应用提供更高的性能。

为深度学习优化过的新型流式多处理器(SM)架构。Volta 对 GPU 核心的 SM 处理器架构进行了重要的重新设计。新的 Volta SM 架构比前代 Pascal 设计能效高 50%,在同样的功率范围下 FP32 和 FP64 性能有重大提升。新的 Tensor Core 是专门为深度学习设计的,为浮点运算速度带来了 12 倍的提升。有了独立的、并行的整型和浮点型数据通路,Volta SM 在负载上也更高效,混合了计算与地址运算。Volta 新的独立线程调度能力使得并行线程之间的细粒度同步协同(finer-grain synchronization and cooperation)成为可能。最终,新型的 L1 Data Cache 与 Shared Memory 子系统的结合也能极大地提升性能,同时还简化了编程。

GV100 GPU 硬件架构

装备有 Volta GV100 GPU 的英伟达 Tesla V100 加速器是目前世界上速度最快的并行计算处理器。GV100 的硬件创新十分显著,除了为 HPC 系统和应用提供远比现在更强的计算能力(如图 3 所示)之外,它还可以大大加快深度学习算法和框架的运行速度。

在各种 HPC 任务中,Tesla V100 平均比 Tesla P100 快 1.5 倍。(该性能基于 Tesla V100 原型卡)

Tesla V100 可以提供业界领先的浮点和整型计算性能。峰值计算速度(基于 GPU Boost 时钟频率):

双精度浮点(FP64)运算性能:7.5 TFLOP/s;

单精度(FP32)运算性能:15 TFLOP/s;

混合精度矩阵乘法和累加:120 Tensor TFLOP/s。

与前一代 Pascal GP100 GPU 类似,GV100 GPU 由多个图形处理集群(Graphics Processing Cluster,GPC)、纹理处理集群(Texture Processing Cluster,TPC)、流式多处理器(Streaming Multiprocessor,SM)以及内存控制器组成。一个完整的 GV100 GPU 由 6 个 GPC、84 个 Volta SM、42 个 TPC(每个 TPC 包含了 2 个 SM)和 8 个 512 位的内存控制器(共 4096 位)。每个 SM 有 64 个 FP32 核、64 个 INT32 核、32 个 FP64 核与 8 个全新的 Tensor Core。同时,每个 SM 也包含了 4 个纹理处理单元。

带有 84 个 SM 单元的完整 Volta GV100

加上 84 个 SM,一个完整的 GV100 GPU 总共有 5376 个 FP32 核、5376 个 INT32 核、2688 个 FP64 核、672 个 Tensor Core 与 336 个纹理单元。每块内存控制器都连接了一个 768 KB 的 2 级缓存,每个 HBM2 DRAM 堆栈都由一对内存控制器控制。一个完整的 GV100 GPU 包括了总共 6144 KB 的二级缓存。图 4 展示了一个带有 84 个 SM 单元的完整 GV100 GPU(不同产品可以使用不同的 GV100 配置)。Tesla V100 加速器使用了 80 个 SM 单元。

Tesla V100 与过去五年历代 Tesla 加速器的参数对比

Volta SM(流式多处理器)

为提供更高的性能而设计的架构,Volta SM 比过去的 SM 设计有更低的指令与缓存延迟,也包括加速深度学习应用的新特性。

主要特性包括:

为深度学习矩阵计算建立的新型混合精度 FP16/FP32 Tensor Core。

为更高的性能、更低的延迟而增强的 L1 数据缓存。

为更简单的解码而改进的指令集,并减少了指令延迟。

更高的速度和能效。

Volta GV100 SM

增强的 L1 数据缓存和共享显存

Volta SM 的 L1 数据缓存和共享显存子系统的组合能显著提高性能,同时也简化了编程并减少了达到或接近峰值应用性能所需的时间成本。

在共享显存块中进行集成可确保 Volta GV100 L1 缓存具有比过去英伟达 GPU 中的 L1 高速缓存更低的延迟和更高的带宽。L1 Volta 作为流式数据的高吞吐量导管(conduit),同时为经常复用的数据提供高带宽和低延迟访问,这两个性能都是目前最好的。英伟达表示,这一特性是 Volta 独有的,其提供比以往更强大的性能。

在 Volta 上,这些代码在没有使用共享显存的情况下只有 7%的性能损失,而 Pascal 的性能下降了 30%。虽然共享显存仍然是最佳选择,但新 Volta L1 设计使程序员能够以更少的编程工作而快速获得足够出色的性能。

全新 GV100 与此前各代架构 GPU 的形式比较,GV100 GPU 支持全新的 Compute Capability 7.0。

独立的线程调配

Volta 架构旨在设计为比以前的 GPU 更容易编程,令用户能在更复杂和多样的应用程序上高效地工作。Volta GV100 是第一款支持独立线程调配的 GPU,其在并行线程指令中可以实现细粒度(finer-grain)的同步和协作。Volta 主要的设计目标是减少在 GPU 中运行指令所需的工作量,并在线程合作中实现更大的灵活度,这样从而为细粒度并行算法提供更高的效率。

英伟达同时也展示了他们如何对 SIMT(单指令多线程)做出重大改进以推进 Volta 架构。32 线程内单个独立的 CUDA 核现在只有有限的自主性;线程现在可以在一个细粒度层面上进行同步,并且仍然处于 SIMT 范式下,所以这就意味着更高的整体效率。更重要的是,独立的线程现在可以放弃再重新安排在一起。这就意味着英伟达的 GPU 有一定数量的调度硬件(scheduling hardware)。

Pascal 和早期的英伟达 GPU 在 SIMT warp 执行模式下的线程调配。大写字母代表指令伪代码中的语句。在一个 warp 中不同的分支是序列化的,这样在分支一边的所有语句一起执行以在另一边语句执行前完成。在 else 语句后,warp 中的线程通常会重新映射。

Volta(下方)独立线程调配架构图与 Pascal 和早期的架构(上方)相比较。Volta 会维持每个线程调配的资源,就像程序计数器(PC)和调用堆栈(S)那样,而早期的架构以每个 warp 为单位维持。

Volta 独立线程调配令其可以交叉执行发散分支(divergent branches)的语句。这就允许执行细粒度并行算法,而 warp 内的线程也就能同步和通信。

程序可以使用显式同步来重新令 warp 中的线程收敛

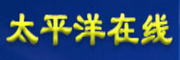

具有细粒度锁(fine-grained locks)的双向链表。在插入结点 B 到链表(右)前,需要获取每一个结点锁(左)

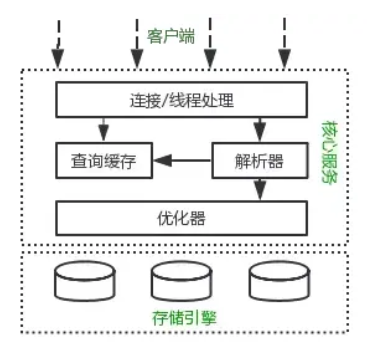

标签: 客户端链表